| XilinxFPGA/CPLD 組み込み 実装 設計製作 VHDL 開発 | |||

■ SPARTAN-3E STARTER KIT

サンプルファイルのプロジェクトを作る

1.新規にプロジェクトを作りビルドする

(0)準備

・ファイルの準備

サンプルファイルをダウンロードして、圧縮ファイルを解凍しておきます。

URLは http://www.xilinx.co.jp/products/boards/s3estarter/reference_designs.htm

ダウンロードするファイルは

Rotary Encoder Interface

s3esk_rotary_encoder_interface.zip というファイルをダウンロードします。

・フォルダの準備

あらかじめプロジェクトファイルを格納するフォルダを適当な名前で作っておきます。

パス、フォルダに使用する文字は半角英数字のみとします。全角文字やスペースなどが入ったパス名、フォルダ名でないことを確認します。

(1)ISEの起動

ISEを起動します。

各々のISEの設定により、前回オープンしていたプロジェクトが自動的に開く場合もあります。

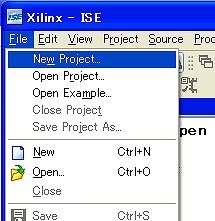

(2)新規プロジェクトウィザード実行

[File]→[New Project]を選択して、New Project Wizard を実行します。

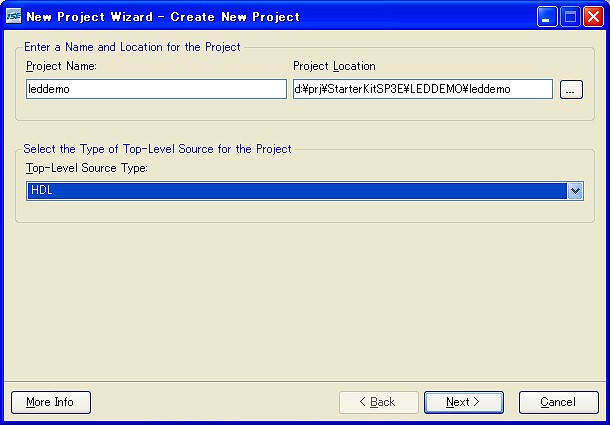

Project Name には適当な名前をつけます。ここでは leddemoとしました。

Project Location にはあらかじめ作っておいたパス名を入力。

Top-Level Source Type には HDLを選択します。

入力がおわったら [Next >]をクリック。

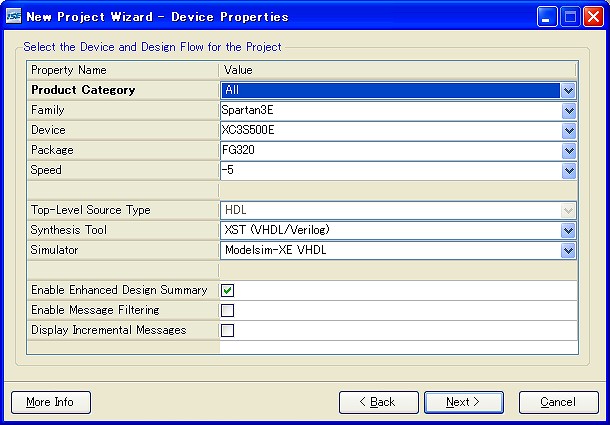

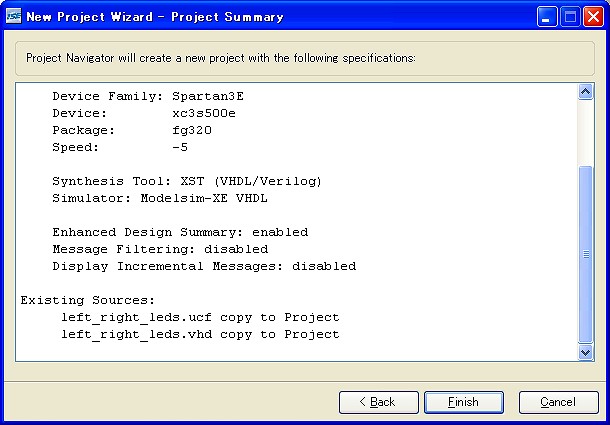

デバイスプロパティを選択します。

Falily : Sparan3E

Device : XC3S500E

Package : FG320

Speed : -5

Synthesis Tool : XST(VHDL/Verilog)

Simulator : 今回は選択されていてもいなくてもかまいません。

下の三つのチェックボックス

- Enable Enhanced Design Summary

- Enable Message Filtering

- Display Incremental Messages

はどちらでもかまいません。

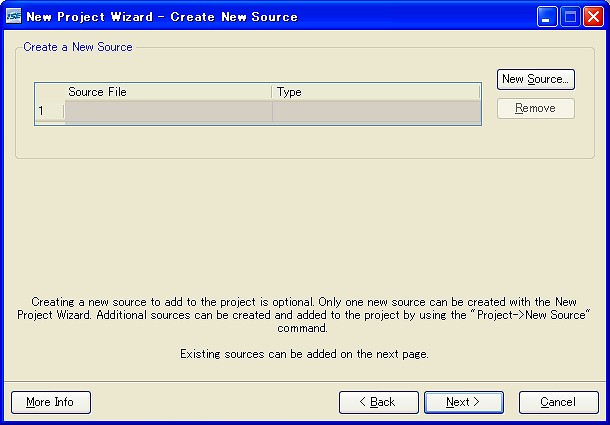

新規ソースファイルを指定する画面です。

今回は新規でソースファイルをコーディングしませんのでなにもせずに[Next >]をクリックします。

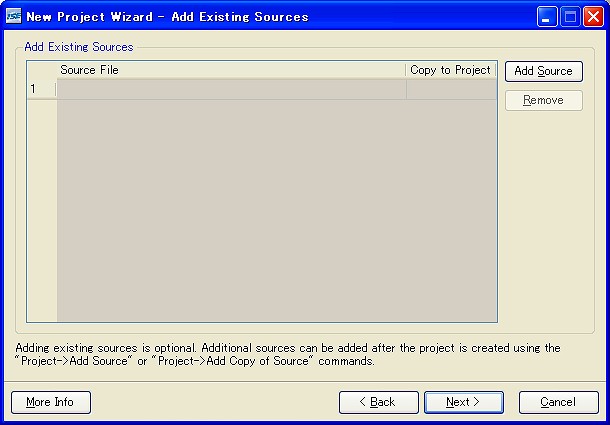

今あるファイルを追加する画面です。

[Add Source]を押します。

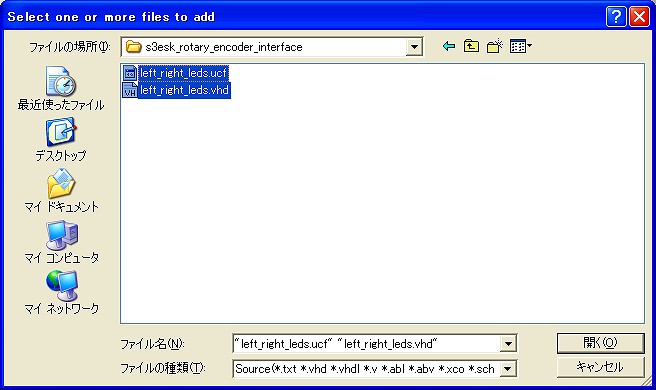

あらかじめ解凍しておいた s3esk_rotary_encoder_interface.zipの中に含まれていたファイルで

タイミング制約ファイルである *.ucf と *.vhdをすべて選択します。

今回は

タイミング制約ファイル : left_right_leds.ucf

VHDLソースファイル : left_right_leds.vdh

の二つのファイルとなります。

選択したら[開く(O)]をクリックします。

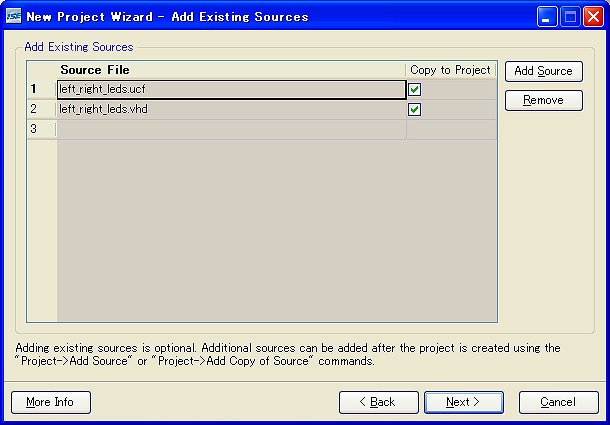

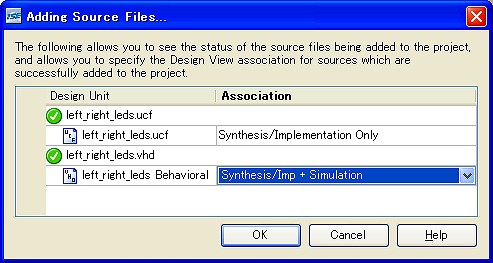

Source File に先ほど選択したファイルがリストアップして表示されています。

Copy to Project のダイアログにチェックがついていることを確認します。

これは選択したファイルをプロジェクトで指定したディレクトリにコピーして使うことを示します。

[Next>]をクリックします。

プロジェクトの設定とプロジェクトのファイルの一覧表示がでます。内容を確認して、問題がなければ [Finish]をクリックします。

left_right_leds.ucf は Synthesis/Implemantation Only とします。

left_right_leds Behavioral は Synthesis/Imp + Simulation とします。

シミュレーションをしない場合 Synthesis/Implementation でもOK。

[OK]をクリックします。

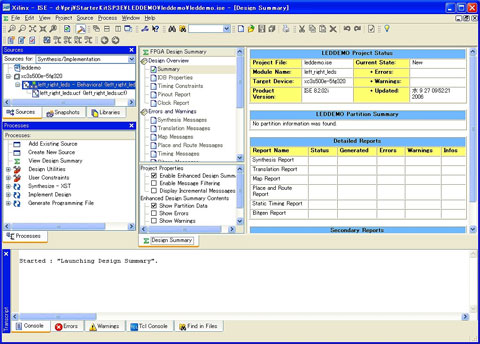

プロジェクトができ上がりました。